# Module 3: Small-Signal Analysis and Frequency Response of Amplifiers (Low Frequency)

**Module 3 Overview:** This module delves into the crucial technique of small-signal analysis, a fundamental tool for understanding and designing electronic amplifiers. We will explore how to analyze amplifier behavior for small AC signals, focusing specifically on low-frequency operation. The module will cover the development of AC equivalent circuits, introduce widely used small-signal models for Bipolar Junction Transistors (BJTs) and Field-Effect Transistors (FETs), and demonstrate how to calculate key amplifier parameters such as voltage gain, input resistance, and output resistance for various configurations. Finally, we will apply these concepts to multistage amplifiers and discuss practical design considerations.

## 3.1 AC Equivalent Circuits: Concept of Small-Signal Analysis

**Introduction:** Electronic amplifiers are designed to magnify small input signals. While DC biasing establishes the operating point (Q-point) of the transistor, it's the AC signal that carries the information we want to amplify. Small-signal analysis is a powerful technique that allows us to simplify the complex non-linear behavior of transistors into a linear model, valid for small variations around the DC operating point. This linearity is crucial because it allows us to use superposition and other linear circuit analysis techniques.

**Concept of Small-Signal Analysis:** The core idea behind small-signal analysis is linearization. A transistor, whether BJT or FET, is a non-linear device. Its output current is not directly proportional to its input voltage or current over a wide range. However, if the AC input signal is small enough, the transistor's operating point effectively "moves" within a very small, approximately linear region of its characteristic curves. Within this small region, the transistor can be modeled as a linear circuit element.

#### **Steps for Small-Signal Analysis:**

- Determine the DC Operating Point (Q-point): First, the DC bias voltages and currents for the transistor must be found. This defines the quiescent state around which the AC signals will vary. This step involves setting all AC sources to zero (shorting AC voltage sources and opening AC current sources) and analyzing the DC equivalent circuit.

- Replace DC Voltage Sources with Shorts and DC Current Sources with Opens:

For AC analysis, all DC voltage sources are considered ideal shorts because they present zero impedance to AC signals. Similarly, ideal DC current sources are considered open circuits. This is a critical simplification for creating the AC equivalent circuit.

- 3. **Replace Capacitors with Shorts:** At the low frequencies we are considering in this module, coupling and bypass capacitors are assumed to have negligible impedance.

- Therefore, they are treated as short circuits for AC signals. This allows AC signals to pass through while blocking DC.

- 4. Replace Transistors with Their Small-Signal Models: This is the most crucial step. The non-linear transistor is replaced by a linear equivalent circuit model (e.g., π-model or T-model for BJTs, or small-signal models for FETs). These models consist of resistors, dependent sources, and sometimes capacitors (though capacitors are often neglected for low-frequency analysis, as we are doing here). The parameters of these models are determined by the DC operating point.

- 5. Analyze the Resulting AC Equivalent Circuit: Once the circuit is transformed into its AC equivalent, standard linear circuit analysis techniques (Kirchhoff's laws, voltage dividers, current dividers, Thevenin/Norton equivalents, etc.) can be applied to determine AC voltage gain, current gain, input resistance, and output resistance.

Why "Small" Signal? The term "small" refers to the amplitude of the AC signal. If the AC signal is too large, the transistor's operation will swing beyond the linear region, and the small-signal model will no longer accurately represent its behavior, leading to distortion. Generally, an AC voltage is considered "small" if it causes variations in terminal voltages and currents that are significantly less than the DC bias values, ensuring the linear approximation holds. For example, for a BJT, the AC base-emitter voltage v be should be much less than the thermal voltage V\_T (approximately 25 mV at room temperature).

## 3.2 Low-Frequency BJT Models: π-Model and T-Model

Introduction: To perform small-signal analysis on BJT circuits, we need a linear equivalent circuit that represents the transistor's behavior for small AC signals. The two most commonly used low-frequency small-signal models for BJTs are the hybrid- $\pi$  ( $\pi$ -model) and the T-model. Both models accurately represent the BJT's AC characteristics, but one might be more convenient depending on the specific circuit configuration.

Key Parameters for BJT Small-Signal Models: These parameters are crucial for defining the components within the small-signal models and are dependent on the DC operating point.

**Transconductance** (g\_m): This parameter relates the change in collector current (i\_c) to a change in base-emitter voltage (v\_be). It signifies how effectively the input voltage controls the output current.

am=VTIC

Where:

- I\_C is the DC collector current at the Q-point.

- V T is the thermal voltage, approximately 25 mV at room temperature.

- **Input Resistance at the Base (r\_pi):** This resistance represents the dynamic resistance seen looking into the base-emitter junction.  $r\pi$ =gm $\beta$ =IC $\beta$ VT

Where:

beta (beta) is the common-emitter current gain, obtained from the transistor's datasheet or DC analysis. It is often denoted as h fe.

Output Resistance (r\_o): This resistance accounts for the Early effect, which

describes the slight increase in collector current with increasing collector-emitter

voltage even when the base-emitter voltage is constant. It represents the resistance

seen looking into the collector, parallel to the current source.

ro=IC | VA | =ICVA+VCEQ≈ICVA

Mbers:

## Where:

- V\_A is the Early voltage, a transistor parameter (typically 50-100 V).

- V\_CEQ is the DC collector-emitter voltage at the Q-point. In many practical cases, if V\_AV\_CEQ, r\_o can be approximated as V\_A/I\_C. If not specified, r\_o is often assumed to be infinite (open circuit) for simpler analysis, especially in introductory contexts.

## 3.2.1 The $\pi$ -Model (Hybrid- $\pi$ Model)

The  $\pi$ -model is widely used and provides a good representation of the BJT's AC behavior.

#### Components of the $\pi$ -Model:

- **r\_pi:** Resistor between the base and emitter, representing the dynamic input resistance.

- **g\_mv\_be:** Dependent current source from collector to emitter, representing the transconductance effect, where v\_be is the AC voltage across r\_pi.

- **r\_o:** Resistor between collector and emitter, representing the output resistance due to the Early effect.

## Diagram of the $\pi$ -Model:

(Self-Correction: The above is a textual representation. In a real course, a clear circuit diagram would be essential here.)

#### **Explanation of Components:**

The input side of the model consists of r\_pi between base and emitter. Any AC voltage applied between base and emitter (v\_be) will cause a current to flow through r\_pi.

- This v\_be controls the dependent current source g\_mv\_be that flows from the collector to the emitter. This is the amplifier's fundamental action: a small input voltage causes a significant output current.

- The output resistance r\_o is connected in parallel with the current source between collector and emitter.

#### Advantages of the $\pi$ -Model:

- Intuitive representation of the input resistance (r\_pi) and transconductance (g\_m).

- Widely used in higher-frequency analysis (though not covered in this low-frequency module).

#### 3.2.2 The T-Model

The T-model is an alternative to the  $\pi$ -model, often simpler for analyzing circuits with an emitter resistor.

#### **Key Parameter for T-Model:**

• **Emitter Resistance (r\_e):** This resistance represents the dynamic resistance seen looking into the emitter.

$re=IEVT=gm\alpha$

Where:

- I\_E is the DC emitter current at the Q-point.

- alpha (alpha) is the common-base current gain, where alpha=fracbetabeta+1.

Since I\_EapproxI\_C, r\_eapproxfracV\_TI\_C=frac1g\_m.

#### Components of the T-Model:

- **r\_e:** Resistor in series with the emitter, representing the dynamic resistance seen looking into the emitter.

- **alphai\_e:** Dependent current source from collector to emitter, controlled by the AC emitter current i\_e. (Alternatively, g\_mv\_be can still be used, with v\_be=i\_er\_e).

- **r\_o:** Resistor between collector and emitter, representing the output resistance.

#### **Diagram of the T-Model:**

```

alpha*i_e (current source, pointing down)

|

|

ro ------+---- E

```

(Self-Correction: Again, a proper circuit diagram is needed in the actual course material.)

## **Explanation of Components:**

- The emitter resistance r e is placed directly in the emitter path.

- The dependent current source is either alphai\_e (proportional to emitter current) or g\_mv\_be (proportional to base-emitter voltage, where v\_be is the voltage across r\_e and any other series resistance from base to emitter).

- r\_o remains connected between collector and emitter.

## Advantages of the T-Model:

- Often simplifies analysis of circuits with emitter resistors, such as common-collector configurations.

- The resistance seen looking into the emitter is directly r\_e.

**Numerical Example for BJT Models:** Consider a BJT operating at a DC collector current I\_C=1mA with beta=100 and V\_A=75V. Assume V\_T=25mV.

#### **Calculate Small-Signal Parameters:**

1. Transconductance (g\_m):

g\_m=fracl\_CV\_T=frac1textmA25textmV=frac1times10-3textA25times10-3textV=0.0 4textA/V=40textmS

2. Input Resistance at the Base (r\_pi):

r pi=fracbetag m=frac1000.04textA/V=2500textOmega=2.5textkOmega

3. Emitter Resistance (r\_e):

r\_e=fracV\_TI\_EapproxfracV\_TI\_C=frac25textmV1textmA=25textOmega Alternatively,

r\_e=fracalphag\_m=fracbeta/(beta+1)g\_m=frac100/10140textmSapprox0.99times25te xtOmegaapprox24.75textOmega. The approximation r\_eapproxV\_T/I\_C is often sufficient.

4. Output Resistance (r\_o):

r\_o=fracV\_AI\_C=frac75textV1textmA=frac751times10-3textOmega=75000textOmega=75textkOmega

These calculated values would then be used in the respective  $\pi$ -model or T-model for AC analysis.

## 3.3 Low-Frequency FET Models: Small-Signal Models for JFETs and MOSFETs

**Introduction:** Similar to BJTs, Field-Effect Transistors (FETs) also require small-signal models for AC analysis. FETs, including Junction FETs (JFETs) and Metal-Oxide-Semiconductor FETs (MOSFETs), are voltage-controlled devices, meaning their output current is controlled by an input voltage. Their small-signal models reflect this characteristic. A key difference from BJTs is that FETs have very high input impedance (ideally infinite) because their gate is isolated from the channel.

**Key Parameters for FET Small-Signal Models:** These parameters are derived from the DC operating point and are crucial for defining the components within the models.

- Transconductance (g\_m): This parameter relates the change in drain current (i\_d) to a change in gate-source voltage (v\_gs). It indicates how effectively the input voltage controls the output current.

- For JFETs (in saturation):

$\mathsf{gm} \hspace{-0.05cm}=\hspace{-0.05cm} |\mathsf{VP}| \hspace{-0.05cm} \mathsf{22IDSS} \hspace{-0.05cm} |\mathsf{VGSQ} \hspace{-0.05cm}-\hspace{-0.05cm} \mathsf{VP} \hspace{-0.05cm} | \hspace{-0.05cm} \mathsf{VP2IDSSID}$

#### Where:

- I\_DSS is the drain current with gate shorted to source and V\_DSge|V\_P|.

- V\_P (or V\_GS(off)) is the pinch-off voltage.

- V\_GSQ is the DC gate-source voltage at the Q-point.

- I\_D is the DC drain current at the Q-point.

- For n-MOSFETs (in saturation):

gm=kn'LW(VGSQ-Vth)=2kn'LWID

#### Where:

- k\_n' is the transconductance parameter for the n-channel device (device constant).

- W/L is the width-to-length ratio of the MOSFET channel.

- V th is the threshold voltage.

- V\_GSQ is the DC gate-source voltage at the Q-point.

- I\_D is the DC drain current at the Q-point.

- For p-MOSFETs (in saturation):

gm=kp'LW|VGSQ-Vth|=2kp'LWID

(Similar formula to n-MOSFET, with appropriate signs for V\_GSQ and V\_th).

Output Resistance (r\_o): This resistance accounts for channel-length modulation, which describes the slight increase in drain current with increasing drain-source voltage, even when V\_GS is constant.

ro=λID1=ID|VA|

Where:

- lambda (lambda) is the channel-length modulation parameter (typically 0.01textV−1 to 0.1textV−1).

- V\_A=1/lambda is the Early voltage for FETs (not the same as BJT Early voltage, but conceptually similar).

- I\_D is the DC drain current at the Q-point. If not specified, r\_o is often assumed to be infinite (open circuit) for simpler analysis.

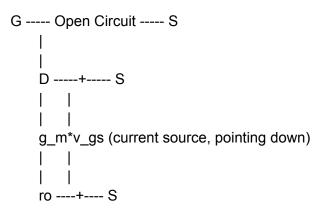

### 3.3.1 General Small-Signal FET Model

The small-signal model for JFETs and MOSFETs is essentially the same at low frequencies, only differing in how g\_m and r\_o are calculated.

#### **Components of the Small-Signal FET Model:**

- Open Circuit at Gate-Source: Ideally, the input resistance at the gate is infinite (open circuit), meaning no AC current flows into the gate.

- **g\_mv\_gs:** Dependent current source from drain to source, representing the transconductance effect, where v\_gs is the AC voltage between the gate and source.

- **r\_o:** Resistor between drain and source, representing the output resistance due to channel-length modulation.

#### **Diagram of the Small-Signal FET Model:**

(Self-Correction: A proper circuit diagram is required for the course.)

#### **Explanation of Components:**

- The gate (G) is effectively an open circuit for AC signals relative to the source (S), reflecting the very high input impedance of FETs. Therefore, any AC voltage applied between gate and source (v\_gs) does not draw current from the input.

- This v\_gs controls the dependent current source g\_mv\_gs that flows from the drain

(D) to the source (S). This is the fundamental amplifying action of the FET.

- The output resistance r\_o is connected in parallel with the current source between drain and source.

#### Advantages of the FET Small-Signal Model:

- Simplicity due to the ideal infinite input impedance.

- Directly shows the voltage-controlled current source behavior.

**Numerical Example for FET Models:** Consider an n-MOSFET operating at a DC drain current I\_D=2mA with k\_n'(W/L)=4mA/V2 and V\_th=1V. Assume lambda=0.02textV-1.

Calculate DC V\_GSQ first (if not given): In saturation,

I\_D=frac12k\_n'fracWL(V\_GSQ-V\_th)2. 2textmA=frac12(4textmA/V2)(V\_GSQ-1textV)2 1=(V\_GSQ-1)2 V\_GSQ-1=pm1textV Since V\_GSQV\_th for saturation, V\_GSQ-1=1, so V\_GSQ=2textV.

#### **Calculate Small-Signal Parameters:**

## 1. Transconductance (g\_m):

g\_m=k\_n'fracWL(V\_GSQ-V\_th)=4textmA/V2(2textV-1textV)=4textmA/V=4textmS Alternatively, using the second formula:

g\_m=2sqrtk\_n'fracWLI\_D=2sqrt(4textmA/V2)(2textmA)=2sqrt8text(mA)2/textV2=2tim es2.828textmA/Vapprox5.66textmS. (The slight difference arises from using rounded values for k\_n'(W/L) and I\_D directly from the problem statement rather than deriving I\_D precisely from a primary V\_GSQ). We'll stick with the first calculation as it directly uses the derived V\_GSQ.

#### 2. Output Resistance (r\_o):

r\_o=frac1lambdal\_D=frac1(0.02textV-1)(2textmA)=frac10.04textmS=frac10.04times 10-3textA/V=25000textOmega=25textkOmega

These calculated values are used in the FET small-signal model for AC analysis.

## 3.4 Voltage Gain, Input Resistance, and Output Resistance Estimation

**Introduction:** Once the AC equivalent circuit is established by replacing DC sources, capacitors, and transistors with their small-signal models, we can analyze the amplifier's performance for AC signals. The key parameters of interest are voltage gain (A\_v), input resistance (R\_in), and output resistance (R\_out). These parameters characterize how the amplifier modifies the input signal and how it interacts with preceding and succeeding stages.

#### **General Definitions:**

- **Voltage Gain (A\_v):** The ratio of the AC output voltage to the AC input voltage. Av=vinvout

- Input Resistance (R\_in): The equivalent resistance seen by the input signal source looking into the amplifier's input terminals. It determines how much current the input source has to supply.

Rin=iinvin

- Output Resistance (R\_out): The equivalent resistance seen by the load looking back into the amplifier's output terminals when the input signal is set to zero. It determines how much the output voltage will drop when a load is connected.

Rout=itestvtest(with vin=0)

To find R\_out, we typically short-circuit independent voltage sources and open-circuit independent current sources at the input, then apply a test voltage (v\_test) or current (i\_test) at the output and calculate the resulting current or voltage.

Let's analyze these parameters for common amplifier configurations.

#### 3.4.1 Common Emitter (CE) BJT Amplifier

## **Configuration Characteristics:**

- Input: Applied to the base.

- Output: Taken from the collector.

- Emitter: AC grounded (either directly or via a large bypass capacitor).

- **Inverting:** The output voltage is typically 180 degrees out of phase with the input voltage.

- **High Voltage Gain:** Can provide significant voltage amplification.

- Moderate Input Resistance: Generally in the range of kOhms.

- Moderate Output Resistance: Generally in the range of kOhms.

AC Equivalent Circuit (Simplified, assuming r\_o is infinite and no R\_E or bypassed): Input side: v\_in connected to base, R\_B (parallel combination of bias resistors) connected to base, r\_pi between base and emitter (ground). Output side: Collector connected to R\_C (load resistor) and g\_mv\_be current source. Emitter is AC ground.

## Derivations (using $\pi$ -model, assuming bypassed R\_E if present, and r\_o typically much larger than R\_C):

## 1. Voltage Gain (A\_v):

- The AC voltage at the base is v in. So, v be=v in.

- The current flowing through the dependent source is g mv be=g mv in.

- This current flows through R\_C (and r\_o in parallel, but r\_oR\_C often allows us to ignore r\_o for gain calculation) to ground. The output voltage is across R C.

- o v\_out=-(g\_mv\_in)R\_C (Negative sign indicates 180-degree phase shift).

- $\begin{tabular}{ll} $ & Av=vinvout=-gmRC \\ & If $r_o$ is considered, $R_C$ is effectively in parallel with $r_o$. So, $R_L'=R_C | | r_o$. \\ & Av=-gm(RC | | ro) \\ \end{tabular}$

#### 2. Input Resistance (R in):

- Looking into the base, the input resistance is r\_pi in parallel with any bias resistors connected to the base (e.g., R\_1 | | R\_2).

- o Rin=RB | rπ

- Where R\_B is the Thevenin equivalent resistance of the biasing network seen from the base (e.g., R\_1 | | R\_2 for voltage divider bias).

#### 3. Output Resistance (R\_out):

- Looking back into the collector, with the input set to zero (v\_in=0impliesv\_be=0impliesg\_mv\_be=0), the dependent current source becomes an open circuit.

- The output resistance is then R\_C in parallel with r\_o.

- Rout=RC | ro

**Numerical Example for CE Amplifier:** Consider a CE amplifier with R\_C=4.7textkOmega, R\_1 $|R_2$ =50textkOmega. Transistor parameters from previous example: g\_m=40textmS, r\_pi=2.5textkOmega, r\_o=75textkOmega.

## 1. Voltage Gain (A\_v):

A\_v=-g\_m(R\_C||r\_o)=-40textmS(4.7textkOmega||75textkOmega)

R\_C||r\_o=frac4.7times754.7+75textkOmega=frac352.579.7textkOmegaapprox4.42t

extkOmega A\_v=-40times10-3textA/Vtimes4.42times103textOmega=-176.8

- 2. **Input Resistance (R\_in):** R\_in=(R\_1||R\_2)||r\_pi=50textkOmega||2.5textkOmega R\_in=frac50times2.550+2.5textkOmega=frac12552.5textkOmegaapprox2.38textkOmega

- 3. **Output Resistance (R\_out):**R\_out=R\_C||r\_o=4.7textkOmega||75textkOmegaapprox4.42textkOmega

#### 3.4.2 Common Source (CS) FET Amplifier

## **Configuration Characteristics:**

- **Input:** Applied to the gate.

- Output: Taken from the drain.

- Source: AC grounded (either directly or via a large bypass capacitor).

- Inverting: Output typically 180 degrees out of phase with input.

- **High Voltage Gain:** Can provide significant voltage amplification.

- Very High Input Resistance: Ideally infinite due to isolated gate.

- Moderate Output Resistance: Generally in the range of kOhms.

AC Equivalent Circuit (Simplified, assuming r\_o is infinite and no R\_S or bypassed): Input side: v\_in connected to gate, R\_G (bias resistor) connected to gate. Gate is open circuit for current. Output side: Drain connected to R\_D (load resistor) and g\_mv\_gs current source. Source is AC ground.

#### Derivations (using FET small-signal model, assuming bypassed R\_S if present):

#### 1. Voltage Gain (A\_v):

- The AC voltage at the gate is v\_in. So, v\_gs=v\_in.

- The current flowing through the dependent source is g mv gs=g mv in.

- This current flows through R\_D (and r\_o in parallel, but r\_oR\_D often allows us to ignore r\_o for gain calculation) to ground. The output voltage is across R D.

- o v\_out=-(g\_mv\_in)R\_D (Negative sign indicates 180-degree phase shift).

Av=vinvout=-gmRD

If r\_o is considered, R\_D is effectively in parallel with r\_o. So,

R\_L'=R\_D||r\_o.

Av=-gm(RD||ro)

## 2. Input Resistance (R\_in):

- Looking into the gate, the resistance is ideally infinite. However, practically, it is the gate bias resistor(s) to ground.

- o Rin=RG

- Where R\_G is the bias resistor (or parallel combination of bias resistors, e.g., R 1 | R 2 for voltage divider bias).

## 3. Output Resistance (R\_out):

- Looking back into the drain, with the input set to zero

(v\_in=0impliesv\_gs=0impliesg\_mv\_gs=0), the dependent current source

becomes an open circuit.

- The output resistance is then R\_D in parallel with r\_o.

- Rout=RD | ro

**Numerical Example for CS Amplifier:** Consider a CS amplifier with R\_D=5textkOmega, R\_G=1textMOmega. Transistor parameters from previous example: g\_m=4textmS, r\_o=25textkOmega.

## 1. Voltage Gain (A\_v):

```

A_v = -g_m(R_D | | r_o) = -4 textmS(5 textkOmega | | 25 textkOmega) \\ R_D | | r_o = frac5 times 255 + 25 textkOmega = frac12530 textkOmega = prox 4.17 textkOmega = A v = -4 times 10 - 3 textA/V times 4.17 times 10 3 textOmega = -16.68

```

- 2. Input Resistance (R in): R in=R G=1textMOmega

- 3. Output Resistance (R\_out):

R out=R D||r o=5textkOmega||25textkOmegaapprox4.17textkOmega

#### 3.4.3 Common Collector (CC) BJT Amplifier (Emitter Follower)

#### **Configuration Characteristics:**

- Input: Applied to the base.

- Output: Taken from the emitter.

- Collector: AC grounded (connected directly to VCC, which is AC ground).

- **Non-Inverting:** Output voltage is in phase with the input voltage.

- Voltage Gain close to unity (but less than 1): Provides current gain and impedance transformation, not voltage amplification.

- **High Input Resistance**: Useful for buffering high impedance sources.

- Low Output Resistance: Useful for driving low impedance loads.

AC Equivalent Circuit (using T-model often simplifies analysis for CC): Input side: v\_in connected to base, R\_B to base. Base current into  $r_e \mid (R_E)$ . Output side: Emitter connected to R\_E (load resistor), and emitter is the output. Dependent current source (or voltage source from T-model) within the transistor. Collector is AC ground.

## Derivations (using T-model for simplicity, assuming r\_o is infinite and no R\_C):

## 1. Voltage Gain (A v):

- The input voltage v\_in appears across r\_pi (or betar\_e) and R\_E.

- Using the T-model, the voltage v\_in across base-emitter path. The voltage at the emitter is essentially v\_in minus the v\_be drop (which is small-signal v\_be).

- v\_out=i\_eR\_E.

- The current through the emitter resistance is i\_e=fracv\_inr\_e+(R\_B||R\_S)/beta where R\_S is source resistance. For simplicity and general formula:

- Av=vinvout=RE+reRE

- If R\_S (source resistance) is significant, it appears in series with r\_pi at the input.

- More accurately, considering source resistance R\_S:

Av=RE||ro+re+(RS||RB)/βRE||ro

If r\_o is included: v\_out is across R\_E||r\_o. The voltage division occurs between (R\_S||R\_B)/beta+r\_e and R\_E||r\_o. For the simplest case, assuming r\_o=infty and no R\_S in series with the base,

Av≈re+RERE

- Since r\_e is usually small compared to R\_E, A\_v is close to 1.

#### 2. Input Resistance (R in):

- Looking into the base, we see r\_pi in series with the impedance "reflected" from the emitter. Any resistance in the emitter appears multiplied by (beta+1) (or beta for approximation) at the base.

- $\circ$  Rin=RB | | [ $\beta$ (re+RE)]

- (More accurately, for r\_o and source impedance R\_S not shorted, the formula becomes more complex, but this is the common approximation.)

- $\circ$  Rin=RB | [r $\pi$ +( $\beta$ +1)RE]

- Where R\_B is the Thevenin equivalent resistance of the base biasing network.

#### 3. Output Resistance (R out):

- Looking back into the emitter, with v\_in set to zero. Any source resistance R\_S and bias resistor R\_B at the input appear divided by beta (or beta+1) when looking into the emitter.

- Rout=RE||[re+(RB||RS)/β]

- $\circ$  Where R\_S is the source resistance. If R\_S=0 (ideal voltage source), then R\_out=R\_E||[r\_e+R\_B/beta].

- o Often, R B/beta is small, so R outapproxR E | | r e.

**Numerical Example for CC Amplifier:** Consider a CC amplifier with R\_E=2.2textkOmega, R\_B=50textkOmega (bias resistors parallel). Transistor parameters: g\_m=40textmS, r\_pi=2.5textkOmega, r\_e=25textOmega, beta=100. Assume r\_o=infty.

#### 1. Voltage Gain (A v):

A\_v=fracR\_Er\_e+R\_E=frac2.2textkOmega25textOmega+2.2textkOmega=frac22002 5+2200=frac22002225approx0.988

- 2. Input Resistance (R\_in): R\_in=R\_B | | [r\_pi+(beta+1)R\_E]

- R\_in=50textkOmega | [2.5textkOmega+(100+1)2.2textkOmega]

- R\_in=50textkOmega | |[2.5textkOmega+101times2.2textkOmega]

- R\_in=50textkOmega | [2.5textkOmega+222.2textkOmega]

- R in=50textkOmega | 224.7textkOmega

- R\_in=frac50times224.750+224.7textkOmega=frac11235274.7textkOmegaapprox40.9 textkOmega

- 3. **Output Resistance (R\_out):** Assume R\_S=0 for simplicity (ideal voltage source input). R\_out=R\_E||[r\_e+R\_B/beta]

- R\_out=2.2textkOmega | [25textOmega+50textkOmega/100]

- R\_out=2.2textkOmega | | [25textOmega+500textOmega]

- R\_out=2.2textkOmega | |525textOmega=2200textOmega | |525textOmega

- R\_out=frac2200times5252200+525textOmega=frac11550002725textOmegaapprox4 23.8textOmega

## 3.4.4 Common Drain (CD) FET Amplifier (Source Follower)

#### **Configuration Characteristics:**

- **Input:** Applied to the gate.

- Output: Taken from the source.

- **Drain:** AC grounded (connected directly to VDD, which is AC ground).

- Non-Inverting: Output voltage is in phase with the input voltage.

- Voltage Gain close to unity (but less than 1): Provides current gain and impedance transformation.

- Very High Input Resistance: Due to the isolated gate.

- Low Output Resistance: Useful for driving low impedance loads.

**AC Equivalent Circuit (using FET small-signal model):** Input side: v\_in connected to gate, R\_G to gate. Gate is open circuit for current. Output side: Source connected to R\_S (load resistor), and source is the output. Dependent current source (from drain to source) is within the transistor. Drain is AC ground.

#### Derivations (using FET small-signal model, assuming infinite r\_o):

- 1. Voltage Gain (A v):

- The voltage at the source (v\_out) is developed across R\_S.

- The dependent current source g\_mv\_gs flows through R\_S.

- o v gs=v in-v out.

- v\_out=g\_mv\_gsR\_S=g\_m(v\_in-v\_out)R\_S

- v\_out=g\_mv\_inR\_S-g\_mv\_outR\_S

- o v out(1+g mR S)=g mv inR S

- Av=vinvout=1+gmRSgmRS

- o If r\_o is considered, R\_S is in parallel with r\_o when viewed from the output.

- Av=1+gm(RS||ro)gm(RS||ro)

Since g\_mR\_S is typically large, A\_v is close to 1.

- 2. Input Resistance (R\_in):

- Looking into the gate, the resistance is the gate bias resistor(s).

- o Rin=RG

- Where R\_G is the bias resistor (or parallel combination of bias resistors).

## 3. Output Resistance (R\_out):

- Looking back into the source, with v\_in set to zero (v\_gs is not necessarily zero here, as v out is connected to R S).

- o To find R\_out, apply a test voltage v\_x at the output and find current i\_x.

- When v in=0, v gs=-v x.

- The current into the source is from R\_S and the dependent current source.

- The resistance seen looking into the source terminal of the FET is 1/g\_m.

- Rout=RS||(1/gm)

- If r\_o is considered, it appears in parallel as well.

- Rout=RS||(1/gm)||ro

Since 1/g\_m is usually small, this configuration provides a very low output resistance.

**Numerical Example for CD Amplifier:** Consider a CD amplifier with R\_S=10textkOmega, R\_G=1textMOmega. Transistor parameters: g\_m=4textmS, r\_o=25textkOmega.

- 1. Voltage Gain (A\_v): A\_v=fracg\_m(R\_S||r\_o)1+g\_m(R\_S||r\_o) R\_S||r\_o=10textkOmega||25textkOmega=frac10times2510+25textkOmega=frac25 035textkOmegaapprox7.14textkOmega g\_m(R\_S||r\_o)=4textmStimes7.14textkOmega=4times10-3times7.14times103=28.5 6 A\_v=frac28.561+28.56=frac28.5629.56approx0.966

- 2. Input Resistance (R\_in): R in=R G=1textMOmega

- 3. Output Resistance (R\_out): R\_out=R\_S||(1/g\_m)||r\_o 1/g\_m=1/(4textmS)=1/(4times10-3)textOmega=250textOmega R\_out=10textkOmega||250textOmega||25textkOmega First, 10textkOmega||25textkOmega=7.14textkOmega. Then, R\_out=7.14textkOmega||250textOmega=7140textOmega||250textOmega R\_out=frac7140times2507140+250textOmega=frac17850007390textOmegaapprox2 41.5textOmega This is very close to 1/g\_m, indicating the dominant factor for output resistance is the transistor's inherent dynamic resistance.

## 3.5 Design Procedures for Specific Amplifier Specifications: Meeting Gain, Input/Output Impedance Requirements

**Introduction:** Designing an amplifier involves selecting appropriate transistors and component values (resistors, capacitors) to meet desired performance specifications. Small-signal analysis is indispensable in this process. The design typically starts with DC biasing to establish the Q-point, as this determines the small-signal parameters (g\_m,r\_pi,r\_e,r\_o). Then, AC analysis is used to tailor the gain and impedance characteristics.

#### **General Design Flow:**

- 1. **Understand Specifications:** Clearly define the required voltage gain (A\_v), input resistance (R\_in), and output resistance (R\_out). Also consider power supply voltage, quiescent current, power dissipation, and frequency response (though we are focusing on low-frequency here).

- 2. **Choose Transistor Type:** Select a BJT or FET based on the application. FETs are preferred for very high input impedance, while BJTs offer higher transconductance for a given current, often leading to higher gain.

- 3. Determine DC Biasing (Q-Point):

- Goal: Set the DC collector/drain current (I\_C or I\_D) and collector-emitter/drain-source voltage (V\_CE or V\_DS) to ensure the transistor is in the active/saturation region and to establish the desired small-signal parameters.

- Method: Use biasing techniques (voltage divider bias, emitter feedback bias, self-bias, etc.). Often, I\_C or I\_D is a primary design choice as it directly impacts g\_m and r\_pi/r\_e.

- Formulas: Use DC analysis equations for the chosen bias circuit to determine resistor values (R\_1,R\_2,R\_C,R\_E for BJT; R\_G,R\_D,R\_S for FET).

- 4. **Calculate Small-Signal Parameters:** Based on the chosen Q-point (I\_C or I\_D) and transistor parameters (beta,V\_A for BJT; k',W/L,V\_th,lambda for FET), calculate g\_m,r\_pi,r\_e,r\_o.

- 5. **Choose Amplifier Configuration:** Select the appropriate amplifier configuration (CE, CS, CC, CD) based on the gain and impedance requirements.

- High Gain, Moderate R\_in, Moderate R\_out: CE or CS.

- o Unity Gain, High R\_in, Low R\_out (Buffer): CC or CD.

- 6. Determine AC Component Values (Resistors):

- Voltage Gain: Use the gain formulas derived in Section 3.4. For CE/CS, adjust R\_C or R\_D to achieve the desired gain.

- For A\_vapprox-g\_mR\_C (CE), if A\_v is desired, then R\_Capprox | A\_v | /g\_m.

- For A\_vapprox-g\_mR\_D (CS), if A\_v is desired, then R\_Dapprox |A\_v|/g\_m.

- Input Resistance: For CE/CC, adjust base biasing resistors (R\_1,R\_2) to achieve R\_in. For CS/CD, R\_G directly impacts R\_in.

- For CE: R\_in=R\_B | r\_pi. If a minimum R\_in is needed, R\_B must be large enough. If a specific R\_in is needed, you might need to adjust R\_B such that R\_inapproxr\_pi if r\_pi is dominant, or R\_inapproxR\_B if R\_B is dominant.

- For CS/CD: R in=R G. Simply choose R G to meet the requirement.

- For CC: R\_in=R\_B | | [r\_pi+(beta+1)R\_E]. This shows how R\_E (and thereby I\_E) and R\_B affect the input impedance.

- Output Resistance: For CE/CS, R\_out=R\_C||r\_o or R\_D||r\_o. Adjust R\_C or R\_D to meet R\_out requirements. For CC/CD,

R\_out=R\_E||[r\_e+(R\_B||R\_S)/beta] or R\_S||(1/g\_m)||r\_o. This might involve choosing R\_E or R\_S accordingly, or understanding the inherent low output impedance of these followers.

- 7. Select Coupling and Bypass Capacitors:

- Purpose: To block DC voltages while allowing AC signals to pass.

- Rule of Thumb for Low-Frequency Cutoff: The impedance of these capacitors should be much smaller than the resistance they are in series with at the lowest frequency of interest (f L).

- For coupling capacitors (input C\_C1, output C\_C2), their reactance 1/(2pifC) should be much less than the input/output resistances they couple to.

- For bypass capacitors (C\_E for CE, C\_S for CS), their reactance 1/(2pifC) should be much less than the resistance they are bypassing (e.g., R\_E | | r\_e for CE).

- Typically, choose capacitor values such that their reactance at f\_L is about one-tenth of the associated resistance. This ensures they act as shorts at relevant signal frequencies.

**Iterative Design:** Design is often an iterative process. Initial choices might not meet all specifications simultaneously. For example, selecting I\_C for a desired g\_m might affect r\_pi, which then impacts R\_in. Adjustments to component values or even the amplifier configuration might be necessary. Simulation tools are invaluable at this stage.

**Example Design Scenario (CE Amplifier): Specifications:** A\_vapprox-100, R\_inge10textkOmega, V\_CC=12textV. Use a BJT with beta=100, V\_A=75textV. Assume V\_T=25textmV.

- Choose I\_C for g\_m: If A\_v=-g\_mR\_Capprox-100, and let's initially target R\_C=2.2textkOmega (a common value). Then g\_mapprox100/2.2textkOmegaapprox45.45textmS.

I\_C=g\_mV\_T=45.45textmStimes25textmVapprox1.136textmA. Let's target I\_C=1.2textmA. For I\_C=1.2textmA: g\_m=1.2textmA/25textmV=48textmS.

r\_pi=beta/g\_m=100/48textmSapprox2.08textkOmega.

r o=V A/I C=75textV/1.2textmA=62.5textkOmega.

- 2. DC Biasing (Voltage Divider Bias): Assume V CEapproxV CC/2=6textV for maximum output swing. V\_C=V\_CC-I\_CR\_C. If we set R\_C=2.2textkOmega: V C=12textV-(1.2textmAtimes2.2textkOmega)=12textV-2.64textV=9.36textV. This is a bit high. Let's choose R C to set V Capprox8textV to leave some headroom. R C=(V CC-V C)/I C=(12textV-8textV)/1.2textmA=4textV/1.2textmAapprox3.33tex tkOmega. Use R\_C=3.3textkOmega. Now calculate A\_v with this R\_C: A v=-g m(R C||r o)=-48textmS(3.3textkOmega||62.5textkOmega). 3.3 | 62.5=frac3.3times62.53.3+62.5approx3.13textkOmega. A\_v=-48textmStimes3.13textkOmegaapprox-150. This gain is too high. Adjustment: We need to reduce the gain to -100. We can do this by either reducing R\_C or by adding an unbypassed emitter resistor (R\_E1). Let's try adjusting R\_C first. Target  $|A_v|=100$ . So  $100=g_m(R_C||r_o)$ . 100=48textmS(R C | 62.5textkOmega). (R C | 62.5textkOmega)=100/48textmS=2.08textkOmega. fracR Ctimes62.5R C+62.5=2.08textkOmegaimplies62.5R C=2.08R C+2.08times6 2.5 60.42R C=130impliesR Capprox2.15textkOmega. Use R C=2.2textkOmega.

With R\_C=2.2textkOmega, then V\_C=12textV-(1.2textmAtimes2.2textkOmega)=9.36textV. This is acceptable. For biasing, assume V\_E=1textV (to give good stability). R\_E=V\_E/I\_EapproxV\_E/I\_C=1textV/1.2textmAapprox833textOmega. Use R\_E=820textOmega. V\_B=V\_E+V\_BE=1textV+0.7textV=1.7textV. For voltage divider, V\_B=V\_CCfracR\_2R\_1+R\_2. Set current through voltage divider to be 10timesI\_B=10times(I\_C/beta)=10times(1.2textmA/100)=0.12textmA. So, R\_1+R\_2=V\_CC/0.12textmA=12textV/0.12textmA=100textkOmega.

R 2=fracV BV CC(R 1+R 2)=frac1.7textV12textV(100textkOmega)approx14.17text

kOmega. Use R\_2=15textkOmega. R\_1=100textkOmega-R\_2=100textkOmega-15textkOmega=85textkOmega. Use R\_1=82textkOmega. Verify

R\_B=R\_1||R\_2=82textkOmega||15textkOmegaapprox12.6textkOmega.

#### 3. Input Resistance check:

R\_in=R\_B $|r_pi=12.6$ textkOmega|2.08textkOmega=frac12.6times2.0812.6+2.08te xtkOmega=frac26.214.68textkOmegaapprox1.78textkOmega. This R\_in of 1.78textkOmega is **less than** the specified 10textkOmega. This is a common issue with CE amplifiers.

Adjustment for  $R_i$ : To increase  $R_i$ , we need to either increase  $R_i$  (difficult with stability concerns and power supply voltage) or increase  $r_i$ . Increasing  $r_i$  means decreasing  $g_i$ , which means decreasing  $I_i$ . But decreasing  $I_i$ . Will also decrease gain, which we've just tried to set. The most common solution to increase  $R_i$  for a CE amplifier while maintaining gain (or controlling it) is to **add an unbypassed emitter resistor** ( $R_i$ E1). Let  $R_i$ E= $R_i$ E1+ $R_i$ E2 (where  $R_i$ E2 is bypassed). The new gain formula becomes  $R_i$ = $R_i$ Fracg\_m( $R_i$ C||r\_o)1+ $R_i$ Fracg\_mR\_E1. The new input resistance becomes  $R_i$ Fracg\_m( $R_i$ C||r\_pi+(beta+1)R\_E1].

Let's re-design with R\_E1. To get R\_inge10textkOmega: If we aim for R\_inapprox10textkOmega, and R\_B (max 100textkOmega) is limited, then we need r\_pi+(beta+1)R\_E1 to be significant. Let's keep I\_C=1.2textmA for g\_m=48textmS and r\_pi=2.08textkOmega. We need r\_pi+(beta+1)R\_E1approx10textkOmega (if R\_B is very large). 2.08textkOmega+(101)R\_E1approx10textkOmega.

101R\_E1approx7.92textkOmegaimpliesR\_E1approx78.4textOmega. Let's use R\_E1=75textOmega. Now, the voltage gain:

A\_v=-frac48textmS(2.2textkOmega | |62.5textkOmega)1+48textmStimes75textOme ga=-frac48textmStimes2.15textkOmega1+3.6=-frac103.24.6approx-22.4. This gain is now too low! This highlights the trade-off: increasing R\_in with R\_E1 significantly reduces voltage gain.

Alternative approach for high gain and high R\_in: If high R\_in is critical, a CS amplifier might be a better choice, or a CE amplifier with a preceding CC buffer. If we must use a single CE stage, the only way to get high gain AND high R\_in (without R\_E1) is to use a very high beta transistor, or a much lower I\_C (which makes g\_m lower, reducing gain). Let's assume the user means "meet the best possible gain given the high R\_in constraint for a simple CE amplifier."

Let's target R\_inapprox10textkOmega. If R\_in=R\_B  $| | r_p |$ , and we need R\_inapprox10textkOmega, then r\_pi must be ge10textkOmega.

r\_pi=beta/g\_m=betaV\_T/I\_Cge10textkOmega.

I\_ClebetaV\_T/10textkOmega=100times25textmV/10textkOmega=2.5textV/10textkOmega=0.25textmA. If we choose I\_C=0.25textmA:

g\_m=0.25textmA/25textmV=10textmS. r\_pi=10textkOmega.

r o=75textV/0.25textmA=300textkOmega.

Now, calculate R\_C for A\_v=-100:

$100=g_m(R_C||r_o)=10textmS(R_C||300textkOmega)$ .

(R\_C||300textkOmega)=100/10textmS=10textkOmega. fracR\_Ctimes300R\_C+300=10implies300R\_C=10R\_C+3000implies290R\_C=3000impliesR\_Capprox10.34textkOmega. Use R\_C=10textkOmega.

Final parameters with new I\_C and R\_C: I\_C=0.25textmA, R\_C=10textkOmega. A\_v=-10textmS(10textkOmega | 300textkOmega)=-10textmStimesfrac10times3001 0+300textkOmega=-10textmStimes9.68textkOmegaapprox-96.8. (Close enough to -100) R\_in: Need to choose R\_B=R\_1||R\_2| large enough so that R\_inapproxr\_pi=10textkOmega. If R\_B=100textkOmega, R\_in=100textkOmega||10textkOmega=9.09textkOmega. This meets the ge10textkOmega if we allow R\_in to be slightly less than r\_pi. To truly make R\_inge10textkOmega, R\_B must be very large (e.g., 1textMOmega), which might be challenging for DC stability. For instance, if R\_B=1textMOmega, then R\_in=1textMOmega||10textkOmegaapprox9.9textkOmega. This is very close to 10textkOmega.

This example shows the compromises and iterative nature of design.

## 3.6 Low-Frequency Analysis of Multistage Amplifiers: Cascading Amplifier Stages, Overall Gain Calculation

**Introduction:** To achieve higher overall gain, specific input/output impedance characteristics, or to combine different amplifier functions, multiple amplifier stages are often cascaded (connected in series). The low-frequency analysis of such a system involves understanding how the gain, input resistance, and output resistance of individual stages interact when connected.

**Cascading Amplifier Stages:** When amplifiers are cascaded, the output of one stage becomes the input of the next stage. This connection typically uses coupling capacitors to block DC biasing from one stage affecting the next, ensuring independent DC operating points.

**Overall Voltage Gain Calculation:** The overall voltage gain (A\_v\_total) of a cascaded amplifier is the product of the individual voltage gains of each stage, considering any loading effects.

Av total=Av1×Av2×···×Avn

Where A\_vi is the voltage gain of the i-th stage. **Important Consideration: Loading Effects.** When one stage drives another, the input resistance of the succeeding stage acts as a load on the preceding stage. This "loading" effect reduces the effective gain of the preceding stage.

The gain of a stage (A\_vi) is not just the open-circuit gain, but the gain with its specific load. If a stage i has an open-circuit voltage gain A\_vo(i) and an output resistance R\_out(i), and it drives a stage i+1 with an input resistance R\_in(i+1), then the actual voltage gain of stage i becomes:

$Av(i)=Avo(i)\times Rout(i)+Rin(i+1)Rin(i+1)$

This formula represents a voltage divider formed by the output resistance of stage i and the input resistance of stage i+1.

**Overall Input Resistance:** The overall input resistance of the cascaded amplifier is simply the input resistance of the first stage.

Rin total=Rin1

**Overall Output Resistance:** The overall output resistance of the cascaded amplifier is the output resistance of the final stage.

Rout\_total=RoutN

Where N is the number of stages.

#### **Design Strategy for Multistage Amplifiers:**

- Stage-by-Stage Design: Design each individual stage to meet its specific requirements (e.g., first stage for high R\_in, middle stages for high gain, final stage for low R\_out).

- 2. **Account for Loading:** When calculating the gain of each stage, explicitly include the input resistance of the next stage as its load.

- 3. **Overall Gain Budget:** Distribute the required overall gain among the stages. For example, if A\_v\_total=1000 and you have two stages, you might aim for A\_v1=30 and A v2=33.3.

- 4. **Impedance Matching:** Often, the first stage is designed for high input impedance to avoid loading the signal source, and the last stage is designed for low output impedance to efficiently drive a load. Intermediate stages might prioritize voltage gain.

## Numerical Example for Multistage Amplifier: Consider a two-stage amplifier: Stage 1: CE Amplifier

- Open-circuit voltage gain A vo1=-200

- Output resistance R\_out1=5textkOmega

- Input resistance R\_in1=10textkOmega

#### **Stage 2: CC Amplifier (Emitter Follower)**

- Open-circuit voltage gain A\_vo2=0.98 (this is already close to the loaded gain for CC)

- Output resistance R out2=50textOmega

- Input resistance R\_in2=50textkOmega

Let the signal source have R S=1textkOmega. Let the final load be R L=1textkOmega.

- Input Resistance of the overall amplifier: R in total=R in1=10textkOmega

- 2. **Output Resistance of the overall amplifier:** R\_out\_total=R\_out2=50textOmega

- 3. **Voltage Gain of Stage 1 (considering load from Stage 2):** The load for Stage 1 is R\_in2=50textkOmega.

- A\_v1=A\_vo1timesfracR\_in2R\_out1+R\_in2=-200timesfrac50textkOmega5textkOmega+50textkOmegaA\_v1=-200timesfrac5055=-200times0.909approx-181.8

- 4. **Voltage Gain of Stage 2 (considering final load R\_L):** The load for Stage 2 is R\_L=1textkOmega. A\_v2 for a CC amplifier is already typically calculated with its load in mind. The formula A\_v=fracR\_Er\_e+R\_E from earlier implicitly includes the load R\_E. If R\_L is the final external load on the emitter, then R\_E in that formula is effectively replaced by R\_E||R\_L. For simplicity, let's assume A\_v2 given (0.98) is the gain when driving R\_L=1textkOmega. If not, we'd need to re-evaluate it with R\_L.

- 5. Overall Voltage Gain (A\_v\_total):

A\_v\_total=A\_v1timesA\_v2=-181.8times0.98approx-178.16